#

# **Monolithic Metal Oxide Transistors**

Yongsuk Choi,<sup>†,∞</sup> Won-Yeong Park,<sup>‡,∞</sup> Moon Sung Kang,<sup>#</sup> Gi-Ra Yi,<sup>‡</sup> Jun-Young Lee,<sup>‡</sup> Yong-Hoon Kim,<sup>\*,†,§</sup> and Jeong Ho Cho<sup>\*,†,‡</sup>

<sup>†</sup>SKKU Advanced Institute of Nanotechnology (SAINT), <sup>‡</sup>School of Chemical Engineering, and <sup>§</sup>School of Advanced Materials Science and Engineering, Sungkyunkwan University, Suwon 440-746, Republic of Korea and <sup>II</sup> Department of Chemical Engineering, Soongsil University, Seoul 156-743, Republic of Korea. <sup>∞</sup>Y.C. and W.-Y.P. contributed equally to this work.

**ABSTRACT** We devised a simple transparent metal oxide thin film transistor architecture composed of only two component materials, an amorphous metal oxide and ion gel gate dielectric, which could be entirely assembled using room-temperature processes on a plastic substrate. The geometry cleverly takes advantage of the unique characteristics of the two components. An oxide layer is metallized upon exposure to plasma, leading to the formation of a monolithic source—channel—drain oxide layer, and the ion gel gate

dielectric is used to gate the transistor channel effectively at low voltages through a coplanar gate. We confirmed that the method is generally applicable to a variety of sol—gel-processed amorphous metal oxides, including indium oxide, indium zinc oxide, and indium gallium zinc oxide. An inverter NOT logic device was assembled using the resulting devices as a proof of concept demonstration of the applicability of the devices to logic circuits. The favorable characteristics of these devices, including (i) the simplicity of the device structure with only two components, (ii) the benign fabrication processes at room temperature, (iii) the low-voltage operation under 2 V, and (iv) the excellent and stable electrical performances, together support the application of these devices to low-cost portable gadgets, *i.e.*, cheap electronics.

**KEYWORDS:** monolithic thin-film transistor · amorphous metal oxide semiconductors · plasma-induced metallization · cheap electronics

lexible device technologies can create completely new markets for disposable electronics, referred to as cheap electronics. Cheap electronics would be realized only through simple and low-cost device fabrication processes that are done under ambient conditions. At the same time, the cheapness should not compromise the resulting device performance and stability. Solution processing of a variety of semiconductors, including organic molecules,<sup>1–7</sup> polymers,<sup>8–11</sup> carbon nanomaterials,12-17 and colloidal nanomaterials,<sup>18,19</sup> has been developed intensively over the last few decades. The resulting devices, however, often yield performances and operational stabilities that are inferior compared to the corresponding properties of devices prepared using vacuum-processed semiconductors. Alternatively, sol-gelprocessed amorphous metal oxide semiconductors (AOS) show promise for the realization of cheap electronics because both the performance and stability properties of the resulting devices remain high.<sup>20–32</sup> In addition, the amorphous film yields

devices that display reliable reproducible performances over a large integrated area. Moreover, the high optical transparency and good mechanical flexibility of the materials provide additional functionalities to these devices.<sup>25,29,33</sup> Sol-gel-processed AOS devices do, however, suffer from a critical drawback in that sol-gel processes typically require a high annealing temperature to induce the sol-gel reaction; thin films annealed at higher temperatures yield higher conductivities.<sup>20,23,26,27</sup> Unfortunately, this high temperature requirement prohibits the use of the materials with flexible cheap substrates, such as plastic or paper.

Additionally, the inherent complexity of conventional electronic device structures containing multiple functional components can increase the device cost by requiring multiple fabrication steps. For instance, thin film transistors (TFTs), which are a basic functional unit of electronics, require at least three functional elements: the thin film semiconductor channel, the gate dielectric, and the electrodes.<sup>3</sup> These three elements

\* Address correspondence to yhkim76@skku.edu, jhcho94@skku.edu.

Received for review January 30, 2015 and accepted March 16, 2015.

Published online March 16, 2015 10.1021/acsnano.5b00700

© 2015 American Chemical Society

VOL.9 • NO.4 • 4288-4295 • 2015

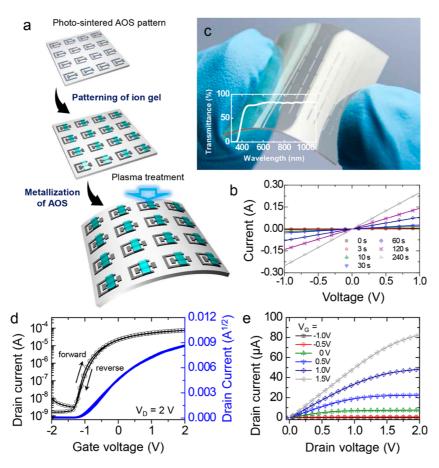

Figure 1. Device fabrication and characterization. (a) Schematic diagram of the monolithic metal oxide transistor fabrication process on a plastic substrate. (b) Current–voltage characteristics of an  $ln_2O_3$  film exposed to Ar plasma for different periods, with increasing Ar plasma treatment of time. (c) Photographic image of the monolithic  $ln_2O_3$  transistor array. The inset shows the optical transmittance of the transistor array. Output (d) and transfer (e) characteristics of a monolithic  $ln_2O_3$  transistor.

are typically formed from three different component materials that require three different processing steps. Although previous efforts have mainly concentrated on the development of new materials and processing methods, even more significant reductions in the device fabrication costs may be achieved by devising an innovative device geometry that allows one to assemble devices in a simpler manner.

To address these issues, we developed a very simple route to fabricating AOS TFTs on plastic substrates through a room-temperature fabrication process.<sup>29</sup> An unconventional transistor structure was devised to allow fabrication of the entire device using only two functional materials: AOS and an electrolyte. The resulting transistors based on amorphous indium oxide (In<sub>2</sub>O<sub>3</sub>) yielded an electron mobility as high as 6.7 cm<sup>2</sup>/V·s under sub-2 V operation. The device also demonstrated a sustained operational stability during bending experiments under ambient conditions. The method could be successfully applied to other AOSs, such as indium-zinc oxide (IZO) or indiumgallium-zinc oxide (IGZO). The proof-of-concept assembly of a basic NOT-logic circuit was demonstrated using the as-prepared In<sub>2</sub>O<sub>3</sub> TFTs. The simple fabrication processes presented here yielded both an

excellent device performance and a good reliability. We believe that these devices have achieved a critical milestone on the path toward realizing cheap flexible electronics.

## **RESULTS AND DISCUSSION**

The simple In<sub>2</sub>O<sub>3</sub> TFT fabrication processes are illustrated in Figure 1a. First, an In<sub>2</sub>O<sub>3</sub> layer was formed through a photochemically driven sol-gel process at room temperature on a plastic substrate.<sup>29</sup> This layer was formed by applying an Al<sub>2</sub>O<sub>3</sub> precoating on a plastic substrate to create a hydrophilic surface that was appropriate for subsequent application of the polar In<sub>2</sub>O<sub>3</sub> precursor solution composed of indium nitrate hydrate dissolved in 2-methoxyethanol. After the precursor solution was spin-coated onto the Al<sub>2</sub>O<sub>3</sub> coated substrate, the film was dried at 60 °C and then irradiated with deep-UV (wavelength = 253.7 and 184.9 nm) to form an In<sub>2</sub>O<sub>3</sub> metal-oxygen-metal network film. Subsequently, the photochemically activated films were patterned using conventional photolithography and etching processes. The patterning process produced patches of a U-shaped In<sub>2</sub>O<sub>3</sub> layer surrounding a hammer-shaped In<sub>2</sub>O<sub>3</sub> layer, which served, respectively, as the coplanar gate and monolithic

VOL. 9 • NO. 4 • 4288-4295 • 2015

www.acsnano.org

source-channel drain of a TFT after the plasma activation process described below.<sup>34</sup> A highly capacitive ion gel gate dielectric (specific capacitance =  $2.2 \,\mu\text{F/cm}^2$ ) based on a poly(ethylene glycol) diacrylate (PEGDA) prepolymer, 2-hydroxy-2-methylpropiophenone (HOMPP) photoinitiator, and 1-ethyl-3-methylimidazolium bis-(trifluoromethanesulfonyl)imide ([EMIM][TFSI]) ionic liquid was partially applied onto the  $In_2O_3$  patches. The ion gel layer formed bridges between the U-shaped and the hammer-shaped patches of the In<sub>2</sub>O<sub>3</sub> layer during UV patterning through a photomask. Subsequently, Ar plasma (200 W) was applied to the substrate to induce metallization of the In<sub>2</sub>O<sub>3</sub> layers<sup>35,36</sup> that were directly exposed to the plasma. X-ray photoelectron spectroscopy (XPS) analysis (Figure S1, Supporting Information) revealed that the exposure of the In<sub>2</sub>O<sub>3</sub> layers to a plasma produced oxygen vacancy sites, which dramatically reduced the resistivity after 4 min of exposure, as shown in the evolution of current-voltage curves (Figure 1b) and transfer curves (Figure S2, Supporting Information). During this process, the patterned ion gel layer played an additional role of as a protection layer for the underlying In<sub>2</sub>O<sub>3</sub> layer. The protection layer prevented direct exposure of In<sub>2</sub>O<sub>3</sub> to Ar plasma, which would have metallized the In<sub>2</sub>O<sub>3</sub>. Consequently, a monolithic hammer-shaped In<sub>2</sub>O<sub>3</sub> patch partially covered with the ion gel layer could be functionalized to produce source (metallized section), channel (protected section), and drain (metallized section) components. Similarly, the neighboring U-shaped In<sub>2</sub>O<sub>3</sub> patch could be functionalized partially to produce a coplanar gate (metallized section). Figure 1c shows a photographic image of a coplanar In<sub>2</sub>O<sub>3</sub> transistor array fabricated on a plastic substrate. The device array displayed an optical transparency of  $\sim$ 80% at 550 nm as shown in the inset.

Within this unique transistor structure, electrons accumulate and flow in the In<sub>2</sub>O<sub>3</sub> channel under a positive applied bias at the coplanar gate voltage upon forming electric double layer (EDL) at the electrolyte/ channel interface.<sup>37</sup> Because the EDL at the interface is formed as long as the electric field is applied across the gate and channel, the EDL could be formed not only in a conventional sandwich-type gating geometry but also in a coplanar gate geometry. Figure 1d shows the transfer characteristics (drain current  $(I_D)$  – gate voltage ( $V_{G}$ )) measured at a constant drain voltage of  $V_{\rm D}$  = 2 V for a coplanar  $\ln_2 O_3$  transistor. The device turned on sharply near  $V_{\rm G} = -1$  V with a subthreshold swing of 130 mV/decade. In addition, the high capacitance of the ion gel gate dielectric (2.2  $\mu$ F/cm<sup>2</sup>) yielded high current ( $\sim$ 0.1 mA) at low operation voltages below 2 V. Negligible current hysteresis between the forward and reverse V<sub>G</sub> traces was observed, indicating a low interfacial trap state density at the ln<sub>2</sub>O<sub>3</sub>/ion gel interface. The statistical distribution of performance properties obtained from 50 monolithic In<sub>2</sub>O<sub>3</sub> transistors

TABLE 1. Summary of Electrical Properties of Monolithic In<sub>2</sub>O<sub>3</sub>, IZO, and IGZO Transistors Including Electron Mobility, on/off Current Ratio, and Threshold Voltage

|           | electron mobility (cm <sup>2</sup> /V·s) | on/off current ratio                      | threshold voltage (V) |

|-----------|------------------------------------------|-------------------------------------------|-----------------------|

| $ln_2O_3$ | 3.6 (±1.2)                               | 5.9 ( $\pm$ 1.6) $	imes$ 10 <sup>4</sup>  | -0.3 (±0.3)           |

| IZ0       | 1.3 (土0.2)                               | 6.5 ( $\pm$ 1.8) $	imes$ 10 $^4$          | $-0.1~(\pm 0.2)$      |

| IGZ0      | 1.6 (±0.3)                               | 7.1 ( $\pm$ 1.4) $\times$ 10 <sup>4</sup> | 0.0 (±0.2)            |

fabricated in different batches is shown in Figure S3 (Supporting Information). The histogram reveals an average electron mobility of 3.6 ( $\pm$ 1.2) cm<sup>2</sup>/V·s, threshold voltage ( $V_{th}$ ) of -0.3 ( $\pm 0.3$ ) V, and on/off current ratio of 5.9 ( $\pm$ 1.6)  $\times$  10<sup>4</sup>. Note that a maximum electron mobility of 6.7  $\text{cm}^2/\text{V} \cdot \text{s}$  was obtained. These results are summarized in Table 1. Figure 1e shows typical output characteristics  $(I_D - V_D)$  of the  $In_2O_3$ transistor under six different applied  $V_{\rm G}$ 's. The device exhibited reasonable gate modulations both in the linear and saturation transistor operation regimes.

We noticed that the carrier mobility of these devices was higher than that obtained from conventional SiO<sub>2</sub>gated field-effect devices (Figure S4, Supporting Information). Typically, higher carrier mobilities were obtained from an AOS system that was gated using an electrolyte gate dielectric, such as an ion gel, compared to the carrier mobilities obtained from conventional SiO<sub>2</sub> gate dielectrics.<sup>38–40</sup> The highly capacitive electrolyte induced a much higher charge density within the channel that filled many carrier traps near the transport level, which in turn, leads to a more efficient charge transport. In addition to this effect, the device geometry of our devices enhanced the carrier mobility. The unique monolithic nature of the sourcechannel-drain geometry of the as-prepared devices improved charge injection from the electrode to the semiconductor or reduced the injection resistance  $(R_{\text{injection}})$  compared to the corresponding values obtained from conventional metal oxide transistors with separate source-drain metal contacts under or on top of the channel. The interfacial properties in the metallized In<sub>2</sub>O<sub>3</sub>/unmetallized In<sub>2</sub>O<sub>3</sub> homojunction in these devices are apparently superior to those obtained in typical metal/In<sub>2</sub>O<sub>3</sub> heterojunctions fabricated with separate metal contacts. Furthermore, the use of a coplanar gate device configuration, such as the configuration described in this work, created metallized source/drain regions positioned within the semiconducting channel plane (Figure 2a) because metallization by an Ar plasma occurred mainly at the top surface of the  $In_2O_3$  layer. The access resistance ( $R_{access}$ ), which represents the resistive character of the device preventing the injected charges from reaching the transport channel, was significantly reduced in our device structure.

These effects were confirmed by evaluating the lumped contact resistance  $(R_c)$  of the monolithic

VOL.9 • NO.4 • 4288-4295 • 2015 ACS

IAI

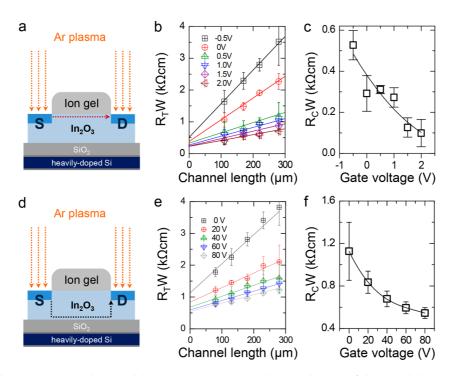

Figure 2. Charge injection in the monolithic  $\ln_2O_3$  transistor. (a) Schematic diagram of the monolithic  $\ln_2O_3$  transistor operated using an ion gel by the coplanar gate. The transport channel was formed at the uppermost region of the  $\ln_2O_3$  film in contact with the ion gel. (b) The channel-width-normalized total resistance  $(R_T)$  of a monolithic  $\ln_2O_3$  transistor plotted as a function of the channel length at different gate voltages. (c) Channel-width-normalized contact resistance  $(R_C)$  extracted from (b), plotted as a function of the gate voltage obtained from (b). (d) Schematic diagram showing the monolithic  $\ln_2O_3$  transistor operated using the bottom SiO<sub>2</sub>/Si gate. The transport channel in this case was formed at the lowermost region of the  $\ln_2O_3$  film in contact with the bottom SiO<sub>2</sub> gate dielectric layer. (e) Channel-width-normalized  $R_T$  for the  $\ln_2O_3$  film gated through the SiO<sub>2</sub> dielectric layer, plotted as a function of the gate voltage. (f) Channel width normalized  $R_C$  extracted from (e) and plotted as a function of the gate voltage.

$In_2O_3$  transistor, which includes both  $R_{injection}$  and Raccess, based on the channel length-dependent resistance of the devices measured using the transmission line method (TLM).41 These measurements were collected using devices fabricated on Si/SiO<sub>2</sub> wafers rather than using those fabricated on PAR substrates. The channel length of the device was varied from 100 to 250  $\mu$ m, while the channel width remained fixed at 1 mm. The channel width normalized total resistance of the transistors is plotted in Figure 2b as a function of the channel length for each  $V_{\rm G}$  value applied to the coplanar gate. The  $R_{\rm C}$  could be extracted from the y-intercept of the linear fit of the total resistance obtained at each  $V_{G}$ . Figure 2c shows the widthnormalized contact resistance  $(R_CW)$  as a function of  $V_{\rm G}$ . The  $R_{\rm C}W$  decreased from 527 to 98  $\Omega$  cm as  $V_{\rm G}$  was varied from -0.5 to 2 V. This value was substantially lower than the values measured from typical MO transistors using conventional metallic contacts<sup>21,35</sup> and was comparable to the homojunctioned IGZO TFTs prepared using H<sub>2</sub> plasma-treated source-drain contacts.<sup>42</sup> Additionally, the values of  $R_{\rm C}$  in the same monolithic In<sub>2</sub>O<sub>3</sub> transistors were measured using TLM again, but this time the gate bias was applied through the bottom Si/SiO<sub>2</sub> gate dielectric. Under a field applied to the bottom gate, the transport channel formed at the very bottom of the In<sub>2</sub>O<sub>3</sub> layer in contact with the

SiO<sub>2</sub> layer, and thus, different  $R_{access}$  values were expected. These results are plotted in Figure 2d,e, and the corresponding *I*–*V* characteristics of the devices are plotted in Figure S5 (Supporting Information). As the In<sub>2</sub>O<sub>3</sub> layer was gated through the bottom, the value of  $R_CW$  varied from 1126 to 546  $\Omega$  cm as  $V_G$  varied from 0 to 80 V. The data obtained from the same set of devices were averaged, so the value of  $R_{injection}$  under both types of gating configurations was assumed to remain constant. The offset was qualitatively attributed to the difference between  $R_{access}$  and the superior accessibility of the charges injected into the transport channel in the ion gel-gated devices.

The operational features of the metallized  $In_2O_3$  coplanar gate and ion gel interface under an applied gate bias were explored. The operation of a gate with the given structure requires contact between the metallized gate and the electrolyte (unlike the operation of a source and drain, which operates better in the absence of contact with the electrolyte). Otherwise, EDL at the gate/electrolyte interface is hardly formed. The ion gel in our device functioned as a protective mask that prevented metallization, suggesting that the metallized gate that was formed within the unmasked  $In_2O_3$  areas and the mask ion gel layer should, in principle, be separated from the electrolyte. In this view, the operational mechanism of the gate may seem

VOL.9 • NO.4 • 4288-4295 • 2015 ACS

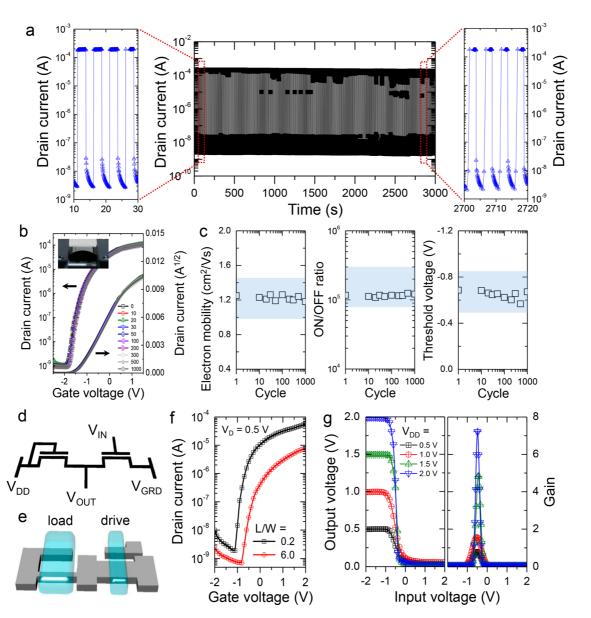

Figure 3. Operational and mechanical stabilities of the monolithic  $In_2O_3$  transistor, and demonstration of a NOT-inverter logic circuit. (a) Evolution of the current level in a monolithic  $In_2O_3$  transistor during continuous cycling between on ( $V_G = 2$  V) and off ( $V_G = -2$  V) states. (b) Evolution of the transfer characteristics of the monolithic  $In_2O_3$  transistor during 1000 fatigue cycles (compressive strain = 0.5%). (c) Changes in the electron mobility, on/off current ratio, and threshold voltage, plotted as a function of the number of compression and release cycles. A circuit diagram (d) and a schematic diagram (e) of an inverter NOT-logic circuit based on two monolithic  $In_2O_3$  transistor ( $L/W = 200 \ \mu m/1000 \ \mu m$ , black) and the load transistor ( $L/W = 300 \ \mu m/50 \ \mu m$ , red). (g) Input–output voltage characteristics of the inverter under various  $V_{DD}$ s and their corresponding gains.

counterintuitive, as direct contact between the metallized gate electrode and the ion gel layer is not present. The device operation, indeed, relies on the swelling of the protective ion gel layer upon exposure to an Ar plasma. As shown in Figure S6 (Supporting Information), the original square-patterned ion gel slowly swelled during the 4 min plasma treatment process. Taking advantage of the swelling of the protective ion gel, metallized  $\ln_2O_3$  formed, even beneath the ion gel layer, especially around the original boundary of the ion gel layer prior to swelling. This boundary zone was exposed to an Ar plasma initially, but it became protected by the swollen ion gel layer upon further plasma treatment. In this manner, direct contact between the metallized gate and the electrolyte could be formed to allow gating of the current levels through the device channel. Because the contacting area of the metallized gate beneath the ion gel layer was small, the capacitance of the ion gel layer in our system was small relative to the capacitances observed in conventional EDL systems.

The realization of practical, cheap, flexible electronics requires low device fabrication costs as well as reliable performance.<sup>26,29,32</sup> The operational and

VOL.9 • NO.4 • 4288-4295 • 2015

AGNANC www.acsnano.org mechanical stabilities of the In2O3 transistors developed were, therefore, investigated. Changes in the transistor characteristics of the In<sub>2</sub>O<sub>3</sub> devices were monitored during continuous on/off switching cycles and mechanical bending cycles. Dynamic stress tests were performed by cycling the devices continuously between on ( $V_G = +2$  V) and off ( $V_G = -2$  V) states while holding  $V_D$  at 2 V. Figure 3a shows the drain-current levels of the devices during the alternating  $V_{\rm G}$  cycles over 1 h. The on/off current ratio of  $\sim 10^5$  remained invariant, even after 500 gate voltage cycles, over a 1 h time period. Next, the mechanical stabilities of the monolithic In<sub>2</sub>O<sub>3</sub> transistors were analyzed by performing cyclic bending tests over 1000 cycles. An In<sub>2</sub>O<sub>3</sub> transistor device array prepared on a plastic substrate was bent (0.5% compressive strain) and relaxed repeatedly. Representative transfer curves measured from the device were collected after a given numbers of cycles, as shown in Figure 3b. No obvious failure or degradation in the operation was observed, even after 1000 bending cycles. The device characteristics, including the electron mobility, on/off current ratio, and threshold voltage of the devices, remained invariant during the bending cycles (Figure 3c). Overall, these results demonstrated that our monolithic In<sub>2</sub>O<sub>3</sub> transistors exhibited stable operational and mechanical properties.

A proof-of-concept demonstration of the In<sub>2</sub>O<sub>3</sub> transistor applicability to logic circuits was conducted by assembling a basic NOT-inverter logic device.<sup>7</sup> Two monolithic  $In_2O_3$  transistors with different channel L/Wratios were connected in series (Figure 3d). The transfer characteristics of the two transistors are shown in Figure 3f, providing evident for differences in the current levels.<sup>43</sup> The transistor with a larger *L/W* ratio  $(L = 300 \ \mu m/W = 50 \ \mu m)$  served as the load while that with the smaller *L/W* ratio ( $L = 200 \ \mu m/W = 1000 \ \mu m$ ) served as the drive of the inverter (Figure 3e). The logic circuit was formed by connecting the load transistor to the supply voltage ( $V_{DD}$ ) and the drive transistor to the ground. The two transistors shared an output terminal. It should be emphasized that these devices were fabricated in three simple steps: formation of In<sub>2</sub>O<sub>3</sub> patches, bridging the patches with ion gel layers, and subsequent Ar plasma treatment. Under a positive  $V_{DD}$ and negative  $V_{IN}$ , the load and drive transistors were present in on and off states, respectively, and thus, the  $V_{OUT}$  signal traced the  $V_{DD}$  value. As the  $V_{IN}$  applied to the drive transistor increased, the drive transistor turned on, and the channel resistance dropped below the resistance of the load transistor. This effect dramatically reduced the  $V_{OUT}$  signal, *i.e.*, the signal inverted. Figure 3g shows the successful inversion of a monolithic In<sub>2</sub>O<sub>3</sub> inverter at different V<sub>DD</sub>'s. As V<sub>DD</sub> was varied from 0.5 to 2 V, the output voltage ( $V_{OUT}$ ) remained comparable to the  $V_{DD}$  at low  $V_{IN}$ . As  $V_{IN}$  increased,  $V_{OUT}$ promptly dropped to 0 V. The signal inversion

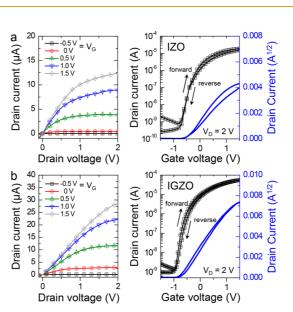

Figure 4. I-V relationships in other monolithic AOS TFTs. Output and transfer characteristics of the monolithic IGZO (a) and IZO (b) TFTs.

(positioned at a negative voltage region) can be manipulated by controlling the  $V_{th}s$  of the transistors. The calculated signal inverter gain ( $dV_{OUT}/dV_{IN}$ ) is displayed in the right panel. The signal inverter gain increased with  $V_{DD}$ , and the maximum gain value exceeded 7 at  $V_{DD} = 2$  V, revealing the successful demonstration of our monolithic  $\ln_2O_3$  transistors for use in simple circuit applications.

Finally, the novel strategy demonstrated here using amorphous  $ln_2O_3$  thin films was successfully applied to other sol-gel-processed AOS systems, including IZO and IGZO. The output and transfer characteristics of the IZO and IGZO transistors prepared using the procedure described above are shown in parts a and b, respectively, of Figure 4. These curves revealed transistor performances that were similar to those of the  $ln_2O_3$ devices. Table 1 summarizes the electrical properties of the different AOS TFTs, including the electron mobility, on/off ratio, and threshold voltage. These results indicated that the method presented here could be generalized for a family of AOS systems.

# CONCLUSION

In conclusion, we demonstrated the fabrication and operation of monolithic metal oxide transistors composed of only two materials for the realization of electrode, channel, and gate dielectric components. These components could be prepared entirely *via* room-temperature processing on plastic substrates. The unique device structure relied on the selective metallization of an oxide layer using plasma and on the coplanar gating of the transistor channel through the ion gel gate dielectric. This geometry was successfully applied to various AOSs, including  $ln_2O_3$ , IZO, and IGZO, and the resulting performances, including the carrier mobility and operational voltage, were superior

VOL.9 NO.4 4288-4295 2015

www.acsnano.org

to those measured in reference devices having a conventional structure. Overall, the simple device geometry allowed fabrication of AOS TFTs without compromising the excellent electrical and mechanical performances of the components. The proposed device geometry and its unique fabrication method constitute a significant contribution toward the realization of cheap, disposable, and flexible electronics.

### **METHODS**

Device Fabrication. A poly-4-vinylphenol (PVP) solution was first prepared by dissolving PVP (1.6 g) and poly(melamine-coformaldehyde) (PMF, 0.8 g) in a propylene glycol monomethyl ether acetate (PGMEA) solvent (18.2 mL). The PVP solution was then spin-coated onto a polyarylate (PAR) flexible substrate (thickness = 200  $\mu$ m) (A200HC, Ferrania Technologies) at 2000 rpm for 60 s, followed by thermal annealing at 120 °C for 12 h inside a vacuum oven to cross-link the PVP. An Al<sub>2</sub>O<sub>3</sub> layer (thickness = 40 nm) was deposited onto the cross-linked PVP/PAR substrate using an atomic layer deposition process and then was treated with UV illumination under an oz1 atm for more than 600 s ( $\lambda_{peak} = 254$  nm, intensity = 28 mW/cm<sup>2</sup>). Separately, a solution of indium oxide precursor was prepared by dissolving 0.1 mol of indium nitrate hydrate (Sigma-Aldrich, 99.999%) in 10 mL of 2-methoxyethanol. The prepared solution was stirred at 75 °C for 12 h and filtered through a 0.2  $\mu$ m PTFE membrane. This precursor solution was spin-coated onto the Al<sub>2</sub>O<sub>3</sub> substrate at 4000 rpm for 30 s and then dried for 2 min on a hot plate (60 °C). The resulting indium oxide layer was sintered using a high-density deep-UV treatment system (UV253H, Filgen) under N<sub>2</sub> flow for 2 h. The resulting indium oxide was patterned through photolithography using an AZ 5214 and AZ 500 MIF developer and was subsequently wet-etched using a 4% LCE-12 solution. The gate dielectric layer was formed by drop-casting an ion-gel solution comprising poly(ethylene glycol) diacrylate (PEGDA, Sigma-Aldrich), 2-hydroxy-2-methylpropiophenone (HOMPP, Sigma-Aldrich), and 1-ethyl-3-methylimidazolium bis(trifluoromethanesulfonyl)imide ([EMIM][TFSI]) ionic liquid (Merck) in a weight ratio of 2:1:22 onto the indium oxide patterned substrate. After drying, the ion gel film was partially exposed to UV (350 W) for 10 s through a photomask. This led to the photoinduced cross-linking of PEGDA to form a gel. The unexposed region was removed by DI water and dried using an air gun. Finally, the entire substrate was exposed to an Ar plasma (200 W, 0.1 Torr) to induce metallization of the In<sub>2</sub>O<sub>3</sub> layer over various treatment times.

**Measurements.** The optical transmittance of the transistor array was characterized using UV–vis spectrophotometry (Agilent 8453). The I-V transistor characteristics were obtained at room temperature under ambient dark conditions using Keithley 2400 equipment and 236 source/measure units.

*Conflict of Interest:* The authors declare no competing financial interest.

Supporting Information Available: Figures S1–S6. This material is available free of charge via the Internet at http:// pubs.acs.org

Acknowledgment. This work was supported by a grant from the Center for Advanced Soft Electronics (CASE) under the Global Frontier Research Program (2013M3A6A5073177), Basic Science Research Program (NRF-2014R1A4A1008474, 2014R1A2A2A01006628, and 2009-0083540) of the National Research Foundation of Korea (NRF) funded by the Ministry of Science, ICT & Future Planning, Korea.

### **REFERENCES AND NOTES**

- 1. Afzali, A.; Dimitrakopoulos, C. D.; Breen, T. L. High-Performance, Solution-Processed Organic Thin Film Transistors from a Novel Pentacene Precursor. J. Am. Chem. Soc. **2002**, *124*, 8812–8813.

- Gelinck, G. H.; Huitema, H. E. A.; Van Veenendaal, E.; Cantatore, E.; Schrijnemakers, L.; Van der Putten, J. B. P. H.;

Geuns, T. C. T.; Beenhakkers, M.; Giesbers, J. B.; Huisman, B. H.; et al. Flexible Active-Matrix Displays and Shift Registers Based on Solution-Processed Organic Transistors. *Nat. Mater.* **2004**, *3*, 106–110.

- Sirringhaus, H. Device Physics of Solution-Processed Organic Field-Effect Transistors. *Adv. Mater.* 2005, *17*, 2411–2425.

- Dickey, K. C.; Anthony, J. E.; Loo, Y. L. Improving Organic Thin-Film Transistor Performance through Solvent-Vapor Annealing of Solution-Processable Triethylsilylethynyl Anthradithiophene. *Adv. Mater.* 2006, *18*, 1721–1726.

- Arias, A. C.; MacKenzie, J. D.; McCulloch, I.; Rivnay, J.; Salleo, A. Materials and Applications for Large Area Electronics: Solution-Based Approaches. *Chem. Rev.* 2010, 110, 3–24.

- Briseno, A. L.; Mannsfeld, S. C. B.; Ling, M. M.; Liu, S. H.; Tseng, R. J.; Reese, C.; Roberts, M. E.; Yang, Y.; Wudl, F.; Bao, Z. N. Patterning Organic Single-Crystal Transistor Arrays. *Nature* 2006, 444, 913–917.

- Gelinck, G.; Heremans, P.; Nomoto, K.; Anthopoulos, T. D. Organic Transistors in Optical Displays and Microelectronic Applications. *Adv. Mater.* 2010, *22*, 3778–3798.

- Pan, H.; Li, Y.; Wu, Y.; Liu, P.; Ong, B. S.; Zhu, S.; Xu, G. Low-Temperature, Solution-Processed, High-Mobility Polymer Semiconductors for Thin-Film Transistors. J. Am. Chem. Soc. 2007, 129, 4112–4113.

- Li, J.; Qin, F.; Li, C. M.; Bao, Q. L.; Chan-Park, M. B.; Zhang, W.; Qin, J. G.; Ong, B. S. High-Performance Thin-Film Transistors From Solution-Processed Dithienothiophene Polymer Semiconductor Nanoparticles. *Chem. Mater.* **2008**, *20*, 2057–2059.

- Li, Y.; Singh, S. P.; Sonar, P. A High Mobility P-type DPP-Thieno[3,2-b]thiophene Copolymer for Organic Thin-Film Transistors. *Adv. Mater.* **2010**, *22*, 4862–4866.

- 11. Li, G.; Zhu, R.; Yang, Y. Polymer Solar Cells. *Nat. Photonics* **2012**, *6*, 153–161.

- Park, H.; Park, J.; Lim, A. K.; Anderson, E. H.; Alivisatos, A. P.; McEuen, P. L. Nanomechanical Oscillations in a Single-C<sub>60</sub> Transistor. *Nature* **2000**, *407*, 57–60.

- Meitl, M. A.; Zhou, Y. X.; Gaur, A.; Jeon, S.; Usrey, M. L.; Strano, M. S.; Rogers, J. A. Solution Casting and Transfer Printing Single-Walled Carbon Nanotube Films. *Nano Lett.* 2004, 4, 1643–1647.

- 14. Geim, A. K.; Novoselov, K. S. The Rise of Graphene. *Nat. Mater.* **2007**, *6*, 183–191.

- Tung, V. C.; Allen, M. J.; Yang, Y.; Kaner, R. B. High-Throughput Solution Processing of Large-Scale Graphene. *Nat. Nanotechnol.* 2009, *4*, 25–29.

- Kobayashi, T.; Kimura, N.; Chi, J.; Hirata, S.; Hobara, D. Channel-Length-Dependent Field-Effect Mobility and Carrier Concentration of Reduced Graphene Oxide Thin-Film Transistors. *Small* **2010**, *6*, 1210–1215.

- Schwierz, F. Graphene Transistors. *Nat. Nanotechnol.* 2010, *5*, 487–496.

- Sun, B.; Sirringhaus, H. Solution-Processed Zinc Oxide Field-Effect Transistors Based on Self-Assembly of Colloidal Nanorods. *Nano Lett.* 2005, *5*, 2408–2413.

- Chung, D. S.; Lee, J. S.; Huang, J.; Nag, A.; Ithurria, S.; Talapin, D. V. Low Voltage, Hysteresis Free, and High Mobility Transistors from All-Inorganic Colloidal Nanocrystals. *Nano Lett.* **2012**, *12*, 1813–1820.

- Kim, H. S.; Byrne, P. D.; Facchetti, A.; Marks, T. J. High Performance Solution-Processed Indium Oxide Thin-Film Transistors. J. Am. Chem. Soc. 2008, 130, 12580–12581.

- Hennek, J. W.; Xia, Y.; Everaerts, K.; Hersam, M. C.; Facchetti, A.; Marks, T. J. Reduced Contact Resistance in Inkjet Printed High-Performance Amorphous Indium Gallium

ARTICLE

Zinc Oxide Transistors. *ACS Appl. Mater. Interfaces* **2012**, *4*, 1614–1619.

- Liu, J.; Buchholz, D. B.; Chang, R. P. H.; Facchetti, A.; Marks, T. J. High-Performance Flexible Transparent Thin-Film Transistors Using a Hybrid Gate Dielectric and an Amorphous Zinc Indium Tin Oxide Channel. *Adv. Mater.* **2010**, *22*, 2333–2337.

- Kim, M. G.; Kanatzidis, M. G.; Facchetti, A.; Marks, T. J. Low-Temperature Fabrication of High-Performance Metal Oxide Thin-Film Electronics *via* Combustion Processing. *Nat. Mater.* 2011, *10*, 382–388.

- 24. Hennek, J. W.; Kim, M. G.; Kanatzidis, M. G.; Facchetti, A.; Marks, T.J. Exploratory Combustion Synthesis: Amorphous Indium Yttrium Oxide for Thin-Film Transistors. J. Am. Chem. Soc. **2012**, *134*, 9593–9596.

- Nomura, K.; Ohta, H.; Takagi, A.; Kamiya, T.; Hirano, M.; Hosono, H. Room-Temperature Fabrication of Transparent Flexible Thin-Film Transistors Using Amorphous Oxide Semiconductors. *Nature* 2004, 432, 488–492.

- Banger, K. K.; Yamashita, Y.; Mori, K.; Peterson, R. L.; Leedham, T.; Rickard, J.; Sirringhaus, H. Low-Temperature, High-Performance Solution-Processed Metal Oxide Thin-Film Transistors Formed by a 'Sol-Gel on Chip' Process. *Nat. Mater.* 2011, *10*, 45–50.

- Han, S. Y.; Herman, G. S.; Chang, C. H. Low-Temperature, High-Performance, Solution-Processed Indium Oxide Thin-Film Transistors. J. Am. Chem. Soc. 2011, 133, 5166– 5169.

- Fortunato, E.; Barquinha, P.; Martins, R. Oxide Semiconductor Thin-Film Transistors: A Review of Recent Advances. *Adv. Mater.* 2012, *24*, 2945–2986.

- Kim, Y. H.; Heo, J. S.; Kim, T. H.; Park, S.; Yoon, M. H.; Kim, J.; Oh, M. S.; Yi, G. R.; Noh, Y. Y.; Park, S. K. Flexible Metal-Oxide Devices Made by Room-Temperature Photochemical Activation of Sol-Gel Films. *Nature* **2012**, *489*, 128–132.

- 30. Jeong, S.; Jeong, Y.; Moon, J. Solution-Processed Zinc Tin Oxide Semiconductor for Thin-Film Transistors. J. Phys. Chem. C **2008**, *112*, 11082–11085.

- Rim, Y. S.; Chen, H. J.; Kou, X. L.; Duan, H. S.; Zhou, H. P.; Cai, M.; Kim, H. J.; Yang, Y. Boost Up Mobility of Solution-Processed Metal Oxide Thin-Film Transistors via Confining Structure on Electron Pathways. *Adv. Mater.* **2014**, *26*, 4273–4278.

- 32. Seo, J. S.; Bae, B. S. Improved Electrical Performance and Bias Stability of Solution-Processed Active Bilayer Structure of Indium Zinc Oxide based TFT. ACS Appl. Mater. Interfaces **2014**, *6*, 15335–15343.

- Hwang, B. U.; Kim, D. I.; Cho, S. W.; Yun, M. G.; Kim, H. J.; Kim, Y. J.; Cho, H. K.; Lee, N. E. Role of Ultrathin Al<sub>2</sub>O<sub>3</sub> Layer in Organic/Inorganic Hybrid Gate Dielectrics for Flexibility Improvement of InGaZnO Thin Film Transistors. *Org. Electron.* **2014**, *15*, 1458–1464.

- Kim, B. J.; Lee, S. K.; Kang, M. S.; Ahn, J. H.; Cho, J. H. Coplanar-Gate Transparent Graphene Transistors and Inverters on Plastic. ACS Nano 2012, 6, 8646–8651.

- Park, J. S.; Jeong, J. K.; Mo, Y. G.; Kim, H. D.; Kim, S. I. Improvements in the Device Characteristics of Amorphous Indium Gallium Zinc Oxide Thin-Film Transistors by Ar Plasma Treatment. *Appl. Phys. Lett.* 2007, *90*.

- Park, J.; Song, I.; Kim, S.; Kim, S.; Kim, C.; Lee, J.; Lee, H.; Lee, E.; Yin, H.; Kim, K. K.; et al. Self-Aligned Top-Gate Amorphous Gallium Indium Zinc Oxide Thin Film Transistors. *Appl. Phys. Lett.* **2008**, *93*.

- Cho, J. H.; Lee, J.; Xia, Y.; Kim, B.; He, Y. Y.; Renn, M. J.; Lodge, T. P.; Frisbie, C. D. Printable Ion-Gel Gate Dielectrics for Low-Voltage Polymer Thin-Film Transistors on Plastic. *Nat. Mater.* 2008, *7*, 900–906.

- Braga, D.; Ha, M. J.; Xie, W.; Frisbie, C. D. Ultralow Contact Resistance in Electrolyte-Gated Organic Thin Film Transistors. *Appl. Phys. Lett.* **2010**, *97*.

- Pu, J.; Yomogida, Y.; Liu, K. K.; Li, L. J.; Iwasa, Y.; Takenobu, T. Highly Flexible MoS<sub>2</sub> Thin-Film Transistors with Ion Gel Dielectrics. *Nano Lett.* **2012**, *12*, 4013–4017.

- 40. Panzer, M. J.; Frisbie, C. D. Polymer Electrolyte Gate Dielectric Reveals Finite Windows of High Conductivity

in Organic Thin Film Transistors at High Charge Carrier Densities. J. Am. Chem. Soc. **2005**, 127, 6960–6961.

- Kim, W. S.; Moon, Y. K.; Kim, K. T.; Lee, J. H.; Ahn, B. D.; Park, J. W. An Investigation of Contact Resistance Between Metal Electrodes and Amorphous Gallium-Indium-Zinc Oxide (a-GIZO) Thin-Film Transistors. *Thin Solid Films* 2010, *518*, 6357–6360.

- Sato, A.; Shimada, M.; Abe, K.; Hayashi, R.; Kumomi, H.; Nomura, K.; Kamiya, T.; Hirano, M.; Hosono, H. Amorphous In-Ga-Zn-O Thin-Film Transistor with Coplanar Homojunction Structure. *Thin Solid Films* **2009**, *518*, 1309–1313.

- Heineck, D. P.; McFarlane, B. R.; Wager, J. F. Zinc Tin Oxide Thin-Film-Transistor Enhancement/Depletion Inverter. *IEEE Electr. Dev. Lett.* 2009, *30*, 514–516.